OQC and Riverlane to Build the UK’s First Quantum Error Corrected Testbed Integrated Within a Data Centre With HPC

UK, April 23, 2025 -- OQC, a global leader in quantum computing and Riverlane, the UK’s leading quantum error correction company, today announced the launch of a project funded by Innovate UK to build the UK’s first Quantum Error Corrected (QEC) testbed integrated within a secure, commercial data centre environment and connected to High Performance Computing (HPC), to be operational by March 2026. This project represents a significant technical development towards the UK Government’s quantum missions, as well as a key step in the commercialisation of quantum computing hardware.

The National Quantum Strategy published in 2023 set out to develop the UK’s strengths across different hardware platforms, software, and components, while reinforcing the government’s intentions to invest in and strengthen the key ecosystem enablers, such as skills, infrastructure, regulation and standards.

The project tangibly supports the UK Government’s ambitious Mission 1 target of achieving the MegaQuop by 2028 and TeraQuop by 2035 by incorporating OQC’s patented technology, the OQC Dimon, into this first-in-kind QEC testbed,significantly advancing quantum error correction through operationalised hardware improvements and enabling access to the system for users.

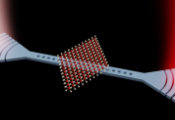

The OQC Dimon is an industry-leading dual-rail qubit design, with which OQC has previously demonstrated a hardware efficient method for reducing the most significant source of error in their quantum computers.

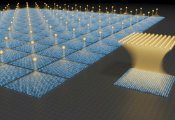

The project will demonstrate a first of its kind Quantum Processing Unit (QPU) with leakage error detection for improved performance with increased hardware-efficiency, it will operationalise the first QEC testbed through integration with HPC within a secure datacentre environment and will include the development of fault-tolerant QEC decoding and resource estimations incorporating real-world noise models of QEC-optimised quantum processors.

The work will target fault-tolerant quantum error correction by isolating the leading cause of errors and incorporating hardware-efficient error correcting protocols. Once operational, this testbed will allow users to:

- Experiment with logical qubits within a secure environment;

- Study short-term noise and long-term variations to improve QEC;

- And bridge the gap between theoretical and practical QEC, providing data to optimise codes and decoders towards achieving the MegaQuop.

The hardware developed via this grant will offer significant improvements over existing quantum processors. Using OQC’s novel Dimon qubit architecture, it can provide x20 improvement in qubit stability while maintaining the same density and form factor as standard superconducting Coaxmon qubits. This is achieved through a dual-rail encoding technology (the use of two physical qubits to encode the quantum information) which enables quantum error detection to enhance operation fidelity.

By also incorporating leakage error detection, developed by Riverlane, the QEC optimised quantum processor enhances performance and hardware efficiency compared to other technologies.