Rigetti and Riverlane Progress Towards Fault Tolerant Quantum Computing With Real-Time and Low Latency Error Correction on Rigetti QPU

BERKELEY, Calif., October 31, 2024 -- Rigetti, a pioneer in full-stack quantum-classical computing, announced the successful demonstration of real-time and low latency quantum error correction on a Rigetti quantum computer.

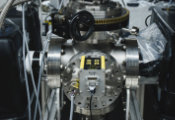

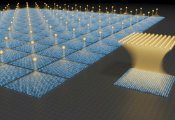

Fault tolerance is the point at which lengthy operations can execute without a single error, due to the application of quantum error correction. Reaching this stage, and in turn realizing the full potential of quantum computers, will require the co-development of quantum error correction and quantum computing technologies. Rigetti and Riverlane’s recent work demonstrating real-time and low-latency quantum error correction on Rigetti’s 84-qubit Ankaa™-2 system is an important step in our journey towards developing fault tolerant quantum computers.

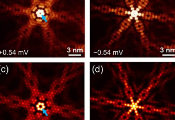

Among the quantum error correction resources being developed are classical algorithms that identify errors that occur during quantum computation. These classical algorithms are known as decoders. A challenge in improving the utility of decoders is addressing the problem of the backlog of computations that accumulates as the decoder processes data. To avoid the backlog problem, the decoding needs to occur at the same speed as the quantum circuit. This experiment demonstrated decoding times faster than the 1\unit\micro threshold for generating measurement data on a superconducting qubit device -- ensuring that the backlog problem is avoided and showcasing that low-latency feedback can be maintained during quantum error correction operations.

“High fidelities are not enough to make a quantum computer useful. There are a lot of classical computing components at play that make the system work, including with error correction. Our partnership with Riverlane to demonstrate quantum error correction technology integrated with our hardware is deeply important on our path towards fault tolerance,” says Dr. Subodh Kulkarni, Rigetti CEO. “A significant benefit of superconducting qubits is that we can attain much higher gate speeds than other modalities. Rigetti’s system gate speeds consistently achieve an active duration of 60-8ns, which is four orders of magnitude faster than systems based on ion traps and pure atoms. System speed is an important factor to enable hybrid computing with current CPUs/GPUs.”

“To execute quantum error correction (QEC) at scale, we need QEC to happen in real-time and on real hardware. Our latest experiment with Rigetti represents a significant step towards these crucial requirements. It demonstrates the ability of Riverlane’s QEC technology to integrate seamlessly with fast-feedback control systems, resulting in the world’s first low-latency QEC experiment. It’s an exciting mark of progress and will help unlock the next generation of quantum experiments that go beyond purely keeping logical qubits alive and into demonstrating the first building blocks of fault-tolerant quantum computing,” says Steve Brierley, Riverlane CEO.

Rigetti’s longtime partnership with Riverlane also includes collaborating on a 24-qubit Ankaa-class system at the UK’s National Quantum Computing Centre where Rigetti will be integrating Riverlane’s technology with the long-term objective of large-scale error correction.