D-Wave Quantum Announces Strategic Development Initiative for Advanced Cryogenic Packaging

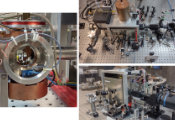

PALO ALTO, Calif., July 30, 2025 - D-Wave Quantum Inc. (“D-Wave”), a leader in quantum computing systems, software, and services, today announced a new strategic development initiative focused on advanced cryogenic packaging. Designed to advance and scale both gate model and annealing quantum processor development, the initiative builds on D-Wave’s technology leadership in superconducting cryogenic packaging and will expand the company’s multichip packaging capabilities, equipment, and processes. By bolstering its manufacturing efforts with state-of-the-art technology, D-Wave aims to accelerate its cross-platform technology development efforts while maintaining and expanding fundamental components of its supply chain.

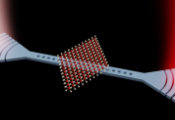

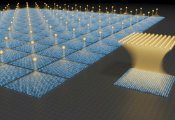

As part of this initiative, D-Wave is leveraging deep expertise and processes at the NASA Jet Propulsion Laboratory (“JPL”), a research and development lab federally funded by NASA and managed by Caltech. Harnessing JPL’s superconducting bump-bond process, D-Wave has demonstrated end-to-end superconducting interconnect between chips, work that D-Wave expects will serve as an important foundation for scaling both D-Wave’s annealing architectures and its fluxonium-based gate-model architectures. D-Wave believes that superconducting bump bonds will be key to the scalable control of fluxonium and to interconnectivity in multichip quantum processor architectures. D-Wave is also acquiring equipment and developing processes with a goal to increase circuit densities in its pioneering superconducting printed-circuit-board (“PCB”) manufacturing, required for both scaling to larger processors and supporting analog-digital quantum computing technology.

“Scaling both annealing and gate-model quantum computers requires high performance packaging,” said Dr. Trevor Lanting, chief development officer at D-Wave. “We believe this strategic initiative will allow us to further extend our leadership position in quantum systems technology development and support our exciting and aggressive product roadmap on the path to 100,000 qubits.”

Packaging quantum processors involves unique and demanding requirements, including: compatibility with ultra-low temperature operation, extremely low magnetic fields, and fully superconducting interconnects with no interruptions in superconductivity all the way from on-chip circuitry through to external control wiring. D-Wave's differentiated solution encompasses cryogenic compatible mechanical and electromagnetic design, regularly achieves lower qubit temperatures than most in the industry, and supports coherence times that meet the requirements for error-corrected gate-model quantum computing technology.