Overcoming the Scale-Up Challenges of Sapphire-Based Quantum Processors

READING, UK – 20th January 2025 – OQC, a global leader in quantum computing solutions and spin-out from Oxford University’s Department of Physics, recently announced their research on the ‘Integration of through-sapphire substrate machining with superconducting quantum processors’. Successful demonstrations of this technique have been shown through the complete manufacturing process of their 32-qubit OQC Toshiko QPU.

The publication illustrates a sapphire machining process which is compatible with high-coherence qubits, facilitating the scaling of quantum processors and paving the way for the development of through-sapphire-vias. This breakthrough research marks a pivotal step for the company and encourages the advancement of superconducting qubit material platforms such as tantalum on sapphire, as well as providing the groundwork for exciting implications in scalability.

The significance for superconducting qubit circuits

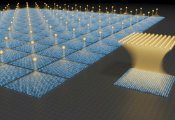

As superconducting qubit circuits become more complex, addressing a large array of qubits presents a significant engineering challenge. With the number of qubits growing, the physical dimensions of the quantum processor unit (QPU) increase, leading to frequency modes that are close or equal to the designed qubit frequencies.

Through-silicon vias (TSVs) have been previously proposed as a promising approach in superconducting qubit arrays to address this issue: they can support densely packed qubit systems without compromising qubit performance or low-loss signal and control routing. Sapphire in particular is a promising substrate for superconducting quantum processors due to its low-loss properties and proven high-coherence substrate platform for transmon qubits. The above mentioned scale-up engineering challenge remains the same for the sapphire platform and becomes even harder to solve, due to the difficulty of realising TSVs in sapphire compared to silicon substrates.

As quantum processors become bigger and more powerful, the package that they sit in increases in size. However, bigger spaces mean lower resonance frequencies, and at some level the package supports frequencies that are the same as the designed qubit ones. As the enclosure becomes larger, these additional modes can disrupt the delicate quantum states of the qubits. This impacts the reliability and accuracy of the computations performed by the processor. Tackling this challenge, and other scaling issues, demands R&D efforts spanning hardware, error correction, control systems, algorithms, fabrication and materials.

Utilising micro-machining as an alternative to etching

Multiple approaches were tested by the research team at OQC in addition to researching the point at which aperture drilling was included in the process flow. The result of which directed them to micromachining. Micro-machining refers to the precise removal of material to create small, intricate structures. This process can involve various methods, such as etching, laser cutting, or mechanical milling, to shape the substrate at sub-mm scales. This technology is common for fabricating MEMS devices, semiconductor components, and photonic circuits.

The process involved protecting the circuit with several layers of different coatings, and actively cooling the substrate during drilling to prevent damage to the substrate and nanofabricated circuits.

This technique not only facilitates the scaling of quantum processors but also paves the way for the development of through-sapphire-vias. These vias can be essential for leveraging the low-loss dielectric properties of sapphire in large-scale QPUs. This advancement was then demonstrated through the complete manufacturing process of OQC’s 32-qubit OQC Toshiko QPU, which is integrated with through-sapphire machining for mode-mitigation purposes. With an end-to-end process, they achieved a 2.5% room temperature resistance spread, which is in-line with the state-of-the-art wafer scale JJ fabrication spread values, without any machining.

The company notes that this exciting development is clear progress in their goal to streamline fabrication and to realise scaling of their QPUs.